## DATA SHEET

# SR8824

CREATE: 29 August 2005 REV. No. 201205-S

#### 24 CHANNEL PARALLEL CORRELATOR CIRCUIT FOR GPS AND GLONASS RECEIVERS

## **FEATURES**

- 24 Fully Independent Correlation Channels

- Switchable to Receive GPS or GLONASS Codes

- Input Multiplexer for Multiple GPS Front-Ends

Allows Antenna Diversity

- Input Multiplexer for GLONASS Multiple (Separate Channels) Front-Ends

- On-Chip Dual UART and Real Time Clock

- □ Fully Compatible with GP2010, GP2015 GPS Receiver Front-End

- Memory and peripheral control logic for AD2106x micro processors

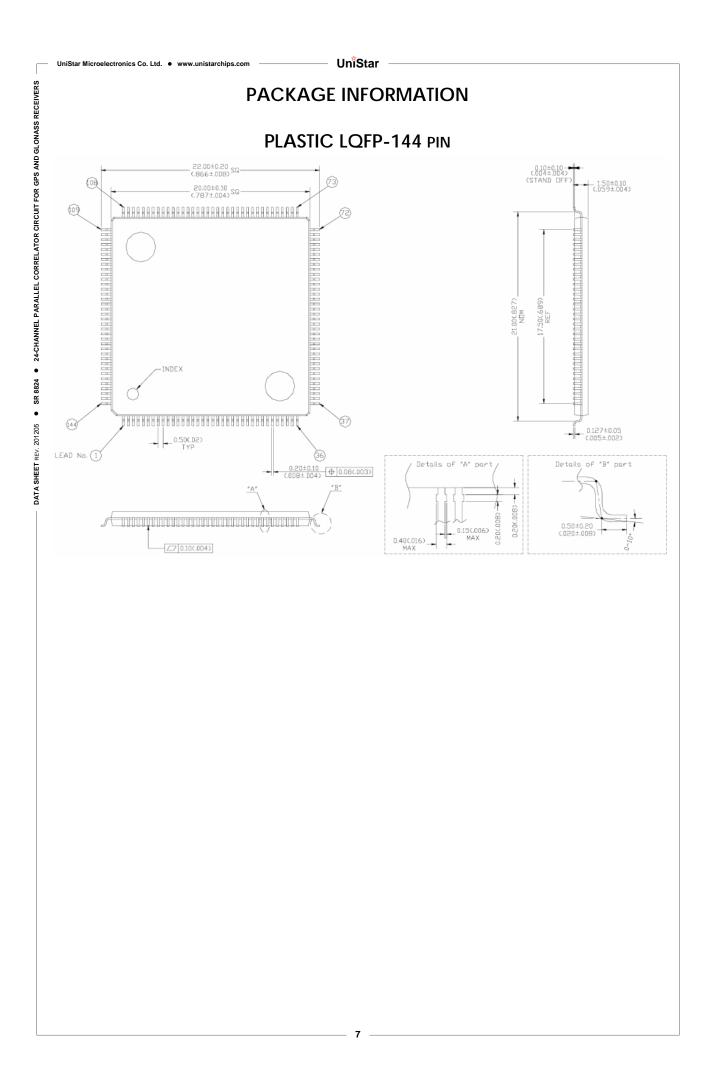

- □ 144-pin Plastic Quad Flatpack

- Power Dissipation Less Than 100mW

## **APPLICATIONS**

UniStar Microelectronics Co. Ltd. • www.unistarchips.com

- GNSS Navigation Systems

- High Integrity Combined Receivers

GNSS Geodetic Receivers

- GNSS Geodetic ReceiversGNSS Time Reference

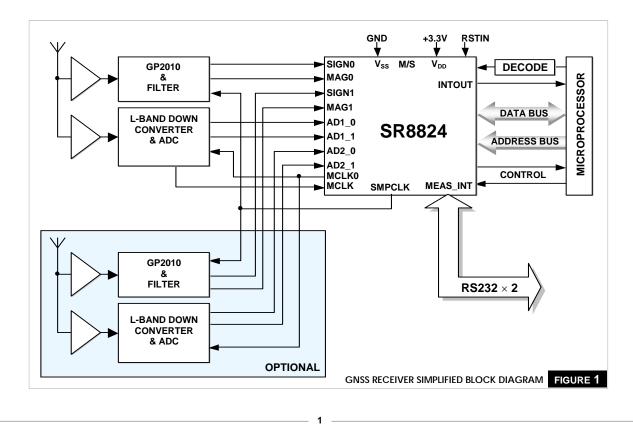

## TYPICAL GNSS RECEIVER (see Fig. 1)

All GPS satellites use the same L1 frequency of 1575·42MHz, but different Gold codes, so a single front-end may be used.

Each GLONASS satellite will use a different 'L1' carrier frequency, in the range 1598.0625 to 1615.500MHz, with 0.5625MHz spacing, but all with

the same 511-bit spreading code, so wide-band receiver used with a single front-end.

To achieve better sky coverage it may be desirable to use more than one antenna, in which case separate front-ends will be needed.

| SYMBOL          | PARAMETER                                 | MIN. | TYP. | MAX. | UNIT |  |

|-----------------|-------------------------------------------|------|------|------|------|--|

| VDD             | I/O supply voltage                        | 2.97 | 3.3  | 3.63 | V    |  |

| V <sub>IH</sub> | Input High Voltage                        | 2.0  | _    | 5.5  | V    |  |

| V <sub>IL</sub> | Input Low Voltage                         | -0.3 | _    | 0.8  | V    |  |

| VT              | Threshold point                           | 1.45 | 1.58 | 1.74 | V    |  |

| VT+             | Schmitt trig Low to High threshold point  | 1.44 | 1.50 | 1.56 | V    |  |

| VT-             | Schmitt trig. High to Low threshold point | 0.89 | 0.94 | 0.99 | V    |  |

| IL              | Input Leakage Current                     | _    | _    | ±10  | μA   |  |

| IOZ             | Tri-State output leakage current          | _    | _    | ±10  | μA   |  |

| RPU             | Pull-up Resistor                          | 39   | 65   | 116  | kΩ   |  |

| RPD             | Pull-down Resistor                        | 40   | 56   | 108  | kΩ   |  |

| V <sub>OL</sub> | Output low voltage IOL=2,424mA            | _    | _    | 0.4  | V    |  |

| V <sub>OH</sub> | Output high voltage IOH=2,424mA           | 2.4  | _    |      | V    |  |

| I <sub>OL</sub> | Low level output current VOL=0.4V 2mA     | 2.4  | 4.0  | 5.0  | mA   |  |

|                 | 4mA                                       | 4.7  | 8.0  | 10   | mA   |  |

|                 | 8mA                                       | 9.4  | 15.9 | 19.8 | mA   |  |

|                 | 12mA                                      | 14.2 | 23.9 | 29.8 | mA   |  |

|                 | 16mA                                      | 18.9 | 31.8 | 39.8 | mA   |  |

|                 | 24mA                                      | 28.3 | 47.8 | 59.7 | mA   |  |

| I <sub>OH</sub> | High level output current VOH=2.4V 2mA    | 2.8  | 5.9  | 9.5  | mA   |  |

|                 | 4mA                                       | 5.6  | 11.9 | 19   | mA   |  |

|                 | 8mA                                       | 11.2 | 23.8 | 38.3 | mA   |  |

|                 | 12mA                                      | 16.8 | 35.7 | 57   | mA   |  |

|                 | 16mA                                      | 22   | 47.7 | 76   | mA   |  |

|                 | 24mA                                      | 33.7 | 71.5 | 115  | mA   |  |

#### **DC CHARACTERISTICS**

### **PIN DESCRIPTIONS**

- **NOTE 1.** 10μF and 0.01μF ceramic bypass capacitor is required to externally connect between VDDint and GND.

- NOTE 2. 4.7 $\mu$ F ceramic bypass capacitor is re-

- NOTE 3. The functions of <u>RW</u> and WEN pins depend on whether the GP1020 is in Motorola<sup>™</sup> (MOT/<u>INTEL</u> = '1') or Intel<sup>™</sup> mode (MOT/<u>INTEL</u> = '0'). In Motorola mode, WEN is an enable (active high) and <u>RW</u> is Read/Write select ('1' = Read). In Intel mode <u>RW</u> is Read, active low, and WEN is Write also active low.

| V <sub>ss</sub>                     | 10, 19, 21, 23, 36, 46, 66, 67, 72, 86, 109, 127, 133, 143 |

|-------------------------------------|------------------------------------------------------------|

| <b>V<sub>DD</sub></b><br>(3.3V)     | 9, 25, 40, 56, 73, 91, 118, 138, 144                       |

| <b>V<sub>DD INT</sub></b><br>(3.3V) | 128, 129                                                   |

| VREF_1.8<br>(Output 1.8V)           | 130                                                        |

| GND                                 | 131, 132                                                   |

**NOTE 4.** WRPROG is used to modify the timing of bus operations; when it is held HIGH the internal write signal is ORed with ALE to allow time for the internal address lines to stabilize; when it is held LOW there is no delay added to write.

NOTE 5. All  $V_{ss}$  and all  $V_{DD}$  pins must be used in order to ensure reliable operation.

#### UniStar

| Microelectronics | Co. Ltd. |  |

|------------------|----------|--|

|                  |          |  |

www.unistarchips.com

UniStar

| PIN<br>No. | PIN NAME         | BUFFER<br>TYPE | DIREC-<br>TION | DES                               | CRIPTION       |                            |  |

|------------|------------------|----------------|----------------|-----------------------------------|----------------|----------------------------|--|

| -          | IED0             | PISUN          | I              | External Data Input 0             |                |                            |  |

|            | IED1             | PISUN          |                | External Data Input 1             |                |                            |  |

|            | IED2             | PISUN          | I              | External Data Input 2             |                |                            |  |

|            | IED3             | PISUN          |                | External Data Input 3             |                | DESCRIPTION                |  |

|            | IED4             | PISUN          | 1              | External Data Input 4             | 0              | F BUFFER TYPE              |  |

| i          | IED5             | PISUN          |                | External Data Input 5             | BUFFER         |                            |  |

|            | IED6             | PISUN          | I              | External Data Input 6             | TYPE           | DESCRIPTION                |  |

|            | IED7             | PISUN          | I              | External Data Input 7             |                | Input pad                  |  |

|            | VDD              |                |                |                                   | PINN           | Input pad                  |  |

| 0          | VSS              |                | 1              |                                   |                |                            |  |

| 1          | ADI2_1           | PIUN           | I              | GL SV Input I2_1                  | PIUN           | Input pad with pull-up     |  |

| 2          | ADQ2_1           | PIUN           |                | GL SV Input Q2_1                  |                |                            |  |

| 3          | ADI2_0           | PIUN           | I              | GL SV Input I2_0                  | PISUN          | Schmitt trigger input page |  |

| 4          | ADQ2_0           | PIUN           | I              | GL SV Input Q2_0                  |                | with pull-up               |  |

| 5          | ADI1_1           | PIUN           | I              | GL SV Input I1_1                  | PRI 16N        | CMOS 3-state output pa     |  |

| 6          | ADQ1_1           | PIUN           | I              | GL SV Input Q1_1                  | DETON          | with input and limited sl  |  |

| 7          | ADI1_0           | PIUN           | I              | GL SV Input I1_0                  |                |                            |  |

| 8          | ADQ1_0           | PIUN           | I              | GL SV Input Q1_0                  |                | rate (16mA)                |  |

| 9          | VSS              |                |                |                                   | POL8N          | CMOS output pad with       |  |

| 0          | CLK40D           | PINN           | 1              | 40 MHz Clock (UART)               |                | limited slew rate (8mA)    |  |

| 1          | VSS              |                |                |                                   | PO8N           | CMOS output pad (8mA       |  |

| 2          | MCLK             | PINN           | I              | 40 MHz Master Clock               |                |                            |  |

| 3          | VSS              |                |                |                                   |                |                            |  |

| 4          | MCLKO            | PO8N           | 0              | 40 MHz Output                     |                |                            |  |

| 5          | VDD              |                |                |                                   |                |                            |  |

| 6          | PMCLK            | PIUN           | I              | Polarity MCLKO                    |                |                            |  |

| 7          | SMPCLK           | PO8N           | 0              | Sampling clock to down-converter  | •              |                            |  |

| 8          | RTCINT           | PISUN          | 1              | Real time clock interrupt input   |                |                            |  |

| 9          | SIGN1            | PIUN           | I              | Satellite Input 1, Sign           |                |                            |  |

| 0          | MAG1             | PIUN           |                | Satellite Input 1, Magnitude      |                |                            |  |

| 1          | SIGN0            | PIUN           | I              | Satellite Input 0, Sign           |                |                            |  |

| 2          | MAG0             | PIUN           |                | Satellite Input 0, Magnitude      |                |                            |  |

| 3          | MS1              | PINN           | I              | ROM addr. pre decode strobe       |                |                            |  |

| 4          | MS3              | PINN           | I              | Correlator addr. pre decode strob | e              |                            |  |

| 5          | MS2              | PINN           | I              | Interfaces addr. pre decode strob |                |                            |  |

| 6          | VSS              |                |                |                                   |                |                            |  |

| 7          | BITECNTL         | POL8N          | 0              | BITE control to down-converter G  | PS             |                            |  |

| 8          | PLLLOCKN         | PIUN           | I              | PLL lock status from down-conve   | ter            |                            |  |

| 9          | GLBIT            | POL8N          | 0              | BITE control to down-converter G  | L              |                            |  |

| 0          | VDD              |                |                |                                   |                |                            |  |

| 1          | PLLLOCKG         | PIUN           | I              | I/P to monitor GLONASS front-en   | d              |                            |  |

| 2          | TMAG             | POL8N          | 0              | Test PRN Pattern Magnitude o/p    |                |                            |  |

| 3          | TSIGN            | POL8N          | 0              | Test PRN Pattern Sign output      |                |                            |  |

| 4          | TICO             | POL8N          | 0              | TIC output from Master            |                |                            |  |

| 5          | PWRRTC           | PIUN           | I              | RTC PWR pin sost                  |                |                            |  |

| 6          | VSS              |                |                |                                   |                |                            |  |

| 7          | RTSA             | POL8N          | 0              | Request To Send UART A            |                |                            |  |

| 8          | DTRA             | POL8N          | 0              | Data Terminal Ready UART A        |                |                            |  |

| 9          | RIA              | PINN           | I              | Ring Indicator UART A             |                |                            |  |

| 0          | CDA              | PINN           | I              | Carrier Detect UART A             |                |                            |  |

| 1          | DSRA             | PINN           | I              | Data Set Ready UART A             |                |                            |  |

| 2          | CTSA             | PINN           | i              | Clear To Send UART A              |                |                            |  |

| 3          | DTRB             | POL8N          | Ō              | Data Terminal Ready UART B        |                |                            |  |

| 4          | OP2A             | POL8N          | Ō              | User Defined output UART A        |                |                            |  |

| 5          | RXA              | PINN           | ĩ              | Receive Data input to Channel A   | of the dual U  | ART                        |  |

| 6          | VDD              |                |                |                                   |                |                            |  |

| 7          | ТХА              | POL8N          | ο              | Transmit Data output from Chann   | el A of the du | al UART                    |  |

| 8          | OP2B             | POL8N          | ŏ              | User Defined output UART B        |                |                            |  |

| 9          | RTSB             | POL8N          | ŏ              | Request To Send UART B            |                |                            |  |

| 0          | CTSB             | PINN           | ĭ              | Clear To Send UART B              |                |                            |  |

| 1          | RIB              | PINN           | i              | Ring Indicator UART B             |                |                            |  |

| 2          | RXB              | PINN           | i              | Receive Data input to Channel B   | of the dual U  | ART                        |  |

| 3          | CDB              | PINN           | i              | Carrier Detect UART B             |                |                            |  |

| 3<br>4     | DSRB             | PINN           | 1              | Data Set Ready UART B             |                |                            |  |

| 4<br>5     | TXB              | PINN<br>POL8N  | 0              | Transmit Data output from Chann   | el B of the du | al LIART                   |  |

| 5<br>6     | VSS              | I- OLOIN       | 0              | Hansmit Data output nom Chann     |                |                            |  |

| ь<br>7     | VSS              |                |                |                                   |                |                            |  |

| 8          |                  | POL8N          | 0              | On/Off control for LNA by CPS     |                |                            |  |

|            | DISCOPN          |                | 0              | On/Off control for LNA by GPS     | 22             |                            |  |

| 9          | DISCOPG<br>TMARK | POL8N          | 0              | On/Off control for LNA by GLONA   |                |                            |  |

| <b>^</b>   |                  | POL16N         | 0              | One pulse per second output       |                |                            |  |

| 0<br>1     | MARKFB           | PIUN           | 1              | Time Mark line driver feedback    |                |                            |  |

- DATA SHEET REV. 201205 • SR 8824 • 24-CHANNEL PARALLEL CORRELATOR CIRCUIT FOR GPS AND GLONASS RECEIVERS

|      | DIN        |                 | DUCCED           | DIPEC          |                                          |

|------|------------|-----------------|------------------|----------------|------------------------------------------|

| LE 1 | PIN<br>No. | SIGNALNAME      | BUFFER<br>TYPE   | DIREC-<br>TION | DESCRIPTION                              |

| INUE | 73         | VDD             |                  |                |                                          |

|      | 74         | CSBT            | POL8N            | 0              | Boot ROM chip select                     |

|      | 75         | WRRTC           | POL8N            | 0              | Write strobe external RTC                |

|      | 76         | RDRTC           | POL8N            | 0              | Read strobe external RTC                 |

|      | 77         | RSTIN           | PINN             | I              | Master Reset (active low)                |

|      | 78         | INTB            | PIUN             |                | External interrupt B                     |

|      | 79         | IRQ             | POL8N            |                | Peripheral devices interrupt request     |

|      | 80         | INTA            | PIUN             | I              | External interrupt A                     |

|      | 81         | WRRS            | POL8N            | 0              | Write strobe external UART               |

|      | 82         | MRES            | POL8N            | 0              | Soft reset external devices              |

|      | 83         | BMS             | PINN             | I              | Boot Memory Select                       |

|      | 84         | CSRTC           | POL8N            | 0              | Chip select external RTC                 |

|      | 85<br>86   | ALERTC<br>VSS   | POL8N            | 0              | Address latch enable external RTC        |

|      | 87         | MEAS_INT        | POL8N            | ο              | Interrupt output to microprocessor       |

|      | 88         | RESET           | POL8N            | Ĭ              | Master Reset (active low)                |

|      | 89         | RESRS           | POL8N            | ò              | Hard reset external devices (High)       |

|      | 90         | INTOUT          | POL8N            | ŏ              | Interrupt out to microprocessor          |

|      | 91         | VDD             |                  | •              |                                          |

|      | 92         | CSB             | POL8N            | 0              | Chip select 2 external UART              |

|      | 93         | CSA             | POL8N            | Ō              | Chip select 1 external UART              |

|      | 94         | RD              | PINN             | Ĩ              | Bus control – read strobe                |

|      | 95         | WR              | PINN             | I              | Bus control – write strobe               |

|      | 96         | WDI             | POL8N            | 0              | Reset external watch Dog                 |

|      | 97         | ACK             | POL8N            | 0              | Data bus ready                           |

|      | 98         | WDO             | PIUN             | I              | External Watch Dog input                 |

|      | 99         | A9              | PINN             | I              | Register Address, bit 9                  |

|      | 100        | A8              | PINN             | I              | Register Address, bit 8 (Test mode, GND) |

|      | 101        | A7              | PINN             | I              | Register Address, bit 7                  |

|      | 102        | A6              | PINN             |                | Register Address, bit 6                  |

|      | 103        | A5              | PINN             | I              | Register Address, bit 5                  |

|      | 104        | A4              | PINN             |                | Register Address, bit 4                  |

|      | 105        | A3              | PINN             | I              | Register Address, bit 3                  |

|      | 106        | A2              | PINN             |                | Register Address, bit 2                  |

|      | 107        | A1              | PINN             | I              | Register Address, bit 1                  |

|      | 108        | A0              | PINN             |                | Register Address, bit 0                  |

|      | 109        | V <sub>SS</sub> |                  | 1/0            | Data Dua hit 0                           |

|      | 110        | D0              | PBL16N           | 1/0            | Data Bus, bit 0                          |

|      | 111        | D1              | PBL16N           | 1/0            | Data Bus, bit 1                          |

|      | 112        | D2              | PBL16N<br>PBL16N | 1/0            | Data Bus, bit 2                          |

|      | 113<br>114 | D3<br>D4        | PBL16N<br>PBL16N | I/O<br>I/O     | Data Bus, bit 3                          |

|      | 114        | D4<br>D5        | PBL16N<br>PBL16N | 1/O            | Data Bus, bit 4<br>Data Bus, bit 5       |

|      | 116        | D5              | PBL16N           | 1/0            | Data Bus, bit 6                          |

|      | 117        | D7              | PBL16N           | 1/O            | Data Bus, bit 7                          |

|      | 118        | VDD             | FBLION           | 1/0            |                                          |

|      | 119        | D8              | PBL16N           | I/O            | Data Bus, bit 8                          |

|      | 120        | D9              | PBL16N           | 1/0            | Data Bus, bit 9                          |

|      | 121        | D10             | PBL16N           | 1/O            | Data Bus, bit 10                         |

|      | 122        | D11             | PBL16N           | 1/0            | Data Bus, bit 11                         |

|      | 123        | D12             | PBL16N           | 1/O            | Data Bus, bit 12                         |

|      | 124        | D13             | PBL16N           | I/O            | Data Bus, bit 13                         |

|      | 125        | D14             | PBL16N           | I/O            | Data Bus, bit 14                         |

|      | 126        | D15             | PBL16N           | I/O            | Data Bus, bit 15                         |

|      | 127        | VSS             |                  |                |                                          |

|      | 128        | VDD INT         |                  |                |                                          |

|      | 129        | VDD INT         |                  |                |                                          |

|      | 130        | VREF_1.8 (Outp  | ut 1.8V)         |                |                                          |

|      | 131        | GND             |                  |                |                                          |

|      | 132        | GND             |                  |                |                                          |

|      | 133        | VSS             | DO: 171          | -              |                                          |

|      | 134        | OED7            | POL12N           | 0              | External Data Output 7                   |

|      | 135        | OED6            | POL12N           | 0              | External Data Output 6                   |

|      | 136        | OED5            | POL12N           | 0              | External Data Output 5                   |

|      | 137        | OED4            | POL12N           | 0              | External Data Output 4                   |

|      | 138        | VDD             |                  | ~              | External Data Output 2                   |

|      | 139        | OED3            | POL12N           | 0              | External Data Output 3                   |

|      | 140        | OED2            | POL12N           | 0              | External Data Output 2                   |

|      | 141        | OED1            | POL12N           | 0              | OExternal Data Output 1                  |

|      | 142        | OED0            | POL12N           | 0              | External Data Output 0                   |

|      | 143        | VSS             |                  |                |                                          |

4

DATA SHEET REV. 201205 • SR 8824 • 24-CHANNEL PARALLEL CORRELATOR CIRCUIT FOR GPS AND GLONASS RECEIVERS

#### FUNCTIONAL DESCRIPTION

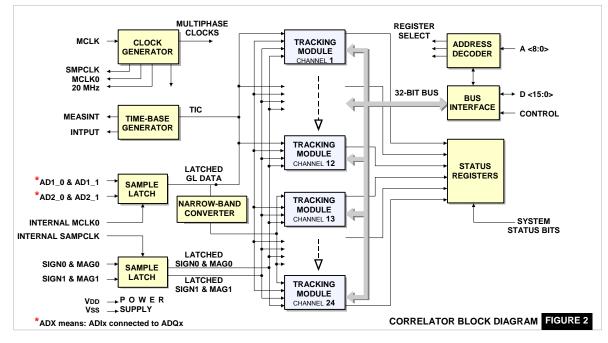

The SR8824 is a 24-channel digital Correlator which may be used to acquire and track the GPS C/A code or the GLONASS signals. The SR8824 incorporates a 24-channel GNSS Correlator.

The SR8824 has on-chip support for the AD2106x 32-bit processors .

12 channels of the SR8824 includes independent digital GLONASS conversion to narrow-band, inde-

pendent digital down-conversion to baseband, C/A and GLONASS code generation, correlation, and accumulate-and-dump registers.

Another 12 channels of the SR8824 don't includes independent digital GLONASS conversion to narrow-band.

Fig. 2 shows a block diagram of the Correlator. It consists of the following blocks:

#### SOFTWARE REQUIREMENTS

The very wide variety of types of GNSS receiver needs to operate the correlator in different ways. So to accommodate this and also to allow dynamic adjustment of loop parameters, the SR8824 has been designed to use software for as many functions as possible. This flexibility means that the device cannot be used without a microprocessor closely linked to it, but as a processor is always needed to convert the output of the SR8824 into useful information this is not a significant limitation.

The software associated with the SR8824 can be divided into two separate modules:

1. Acquire and track satellite signals to give pseudo-ranges.

2. Process pseudo-ranges to give the navigation solution and format it in a form suitable for the user.

For the Navigation Solution to be possible all of the pseudoranges must have exactly the same clock error, which can then be removed iteratively to give real ranges if sufficient satellites are tracked (three if the height is known, otherwise four). This need for exact matching of timing errors explains the need for all of the complicated synchronisation between all 12 channels of the correlator.

The following relates only to the signal processing aspects of the software, to acquire and track signals from up to twelve satellites and to obtain the pseudo-ranges and the navigation message. The operation of the navigation software is not dependent on the details of the correlator, and so does not need to be included in this data sheet.

A pair of on-chip interrupt timebase signals are provided to help implement a data transfer protocol between the microprocessor and the 12-channel correlator at fixed time intervals; these signals are:

- INTOUT used to interrupt the microprocessor to retrieve accumulated data (1.023ms worth) period of interrupt normally less than 1ms.

- 2. MEAS\_INT used to interrupt the microprocessor to retrieve Measurement data that occurs every TIC (approximately 100ms period).

These interrupts can be used to achieve instant response from the microprocessor via an Interrupt Service Routine. Otherwise software based polling scheme will be needed; the choice is set by the application. If the INTOUT interrupt is used, and perhaps also if polling is used, the data transfer rate is about twice the correlation result rate for each channel, so many transfers will not give new data. Examining the status registers before each transfer to see if new data is available and then only reading the data if it is useful can reduce bus use. The very wide variety of types of GNSS receiver needs to operate the correlator in different ways. So to accommodate this and also to allow dynamic adjustment of loop parameters, the SR8824 has been designed to use software for as many functions as possible. This flexibility means that the device cannot be used without a microprocessor closely linked to it, but as a processor is always needed to convert the output of the SR8824 into useful information this is not a significant limitation.

The software associated with the SR8824 can be divided into two separate modules:

1. Acquire and track satellite signals to give pseudo-ranges.

2. Process pseudo-ranges to give the navigation solution and format it in a form suitable for the user.

For the Navigation Solution to be possible all of the pseudoranges must have exactly the same clock error, which can then be removed iteratively to give real ranges if sufficient satellites are tracked (three if the height is known, otherwise four). This need for exact matching of timing errors explains the need for all of the complicated synchronisation between all 12 channels of the correlator.

The following relates only to the signal processing aspects of the software, to acquire and track signals from up to twelve satellites and to obtain the pseudo-ranges and the navigation message. The operation of the navigation software is not dependent on the details of the correlator, and so does not need to be included in this data sheet.

A pair of on-chip interrupt timebase signals are provided to help implement a data transfer protocol between the microprocessor and the 12-channel correlator at fixed time intervals; these signals are:

- INTOUT used to interrupt the microprocessor to retrieve accumulated data (1.023ms worth) period of interrupt normally less than 1ms.

- MEAS\_INT used to interrupt the microprocessor to retrieve Measurement data that occurs every TIC (approximately 100ms period).

These interrupts can be used to achieve instant response from the microprocessor via an Interrupt Service Routine. Otherwise software based polling scheme will be needed; the choice is set by the application. If the INTOUT interrupt is used, and perhaps also if polling is used, the data transfer rate is about twice the correlation result rate for each channel, so many transfers will not give new data. Examining the status registers before each transfer to see if new data is available and then only reading the data if it is useful can reduce bus use.

It is important to note that the timing of each of the correlator channels will be locked to its own incoming signal and not to each other or to the microprocessor interrupts, so new data is generated asynchronously. The sampling instant of measurement data of all channels however is common to give a consistent navigation solution.

In order to acquire lock to the satellites as quickly as possible, the data from the last fix should be stored as a starting point for the next fix. It is also useful to make use of the embedded real-time clock on the chip to give a good estimate of GNSS time for the next fix; the navigation solution can be used to measure clock drift and calculate a correction for the clock to overcome ageing. The user's location (or a good estimate of it) along with the Almanac and the correct time will indicate which satellites should be searched for. These may be used to find an estimate of Doppler effects, while the previous clock error is the best available estimate of the present clock error. If this information is not available then the receiver must scan a much wider range of values, which will greatly increase the time to lock. The satellite Clock Correction and Ephemeris are needed for the navigation solution, so if a recent set is held in memory the calculations may begin as soon as lock is achieved and not need to wait for the Satellite Navigation message re-transmission (18 to 36 seconds).